Die Mikroelektronik benötigt hochleitfähige und stabile Leiterbahnen, oftmals mit der zusätzlichen Bedingung einer hohen Wärmeleitfähigkeit des Substrats für eine robuste Performance der Systeme. Um dem steigenden Kostendruck auszuweichen, werden auch in der Mikroelektronik verschiedene Verfahren zur Einsparung von Materialkosten (Edelmetalle) gekoppelt. Aus der Kombination von beispielsweise Siebdruck und elektrolytischer Beschichtung ergeben sich neue Anforderungen an die Galvanik. In der Arbeitsgruppe wird der Einfluss unterschiedlicher galvanischer Bäder auf verschiedene Siebdruck-Metallisierungen untersucht.

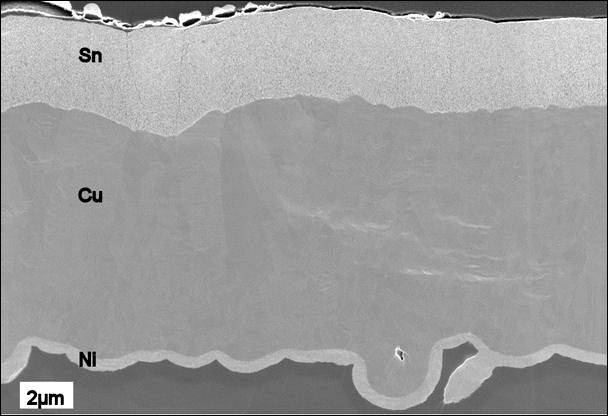

Für die Hochleistungselektronik werden elektrolytische Metallisierungen hochleitfähiger Kupferbahnen mit gleichzeitig hoher Wärmeleitfähigkeit entwickelt. Zur Materialeinsparung bei der Herstellung bondfähiger Goldschichten kommen die chemische Nickel- und die stromlose Goldabscheidung zum Einsatz. Letztere müssen die Dickschichten vollständig abdecken, um eine Bondbarkeit zu gewährleisten.

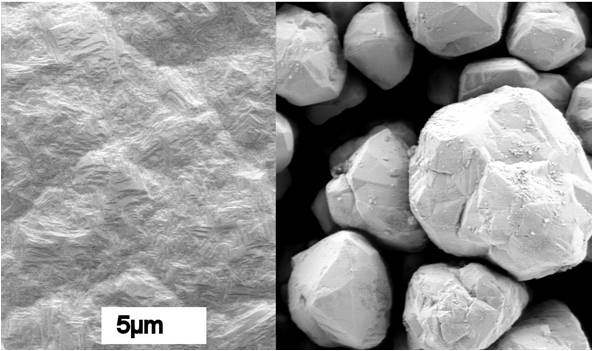

Zum Verschleißschutz und für die Zuverlässigkeit von Gold-Kontakten werden Dispersionsschichten mit keramischen Nanopartikeln entwickelt.

Leistungsangebot

- Verfahrensentwicklung für elektrolytische und stromlose Beschichtungen

- Elektrochemische und mikroskopische Schichtcharakterisierung