Mikroelektronik, die in automobilen Anwendungen eingesetzt wird, unterliegt hohen Belastungen und einer langen Einsatzzeit. Zudem verkleinern sich die Dimensionen aufgrund innovativer Technologien ständig. Daraus ergeben sich neue Erfordernisse hinsichtlich der Zuverlässigkeitsuntersuchung.

Am Fraunhofer IKTS wurde dafür das Zuverlässigkeitsverhalten von führenden »28 nm high-k metal gate CMOS SRAM«-Schaltkreisen (GLOBALFOUNDRIES Dresden) mit aufgebrachter mechanischer Belastung untersucht. Um eine tiefergehende Untersuchung zu gewährleisten, ist ein neuer Test entwickelt worden, der drei Prüfmethoden vereint: ein mechanisches Verfahren mittels Nanoindentation, ein elektrisches Messverfahren und FEM-Simulationen von mechanischer Belastung auf Transistorebene.

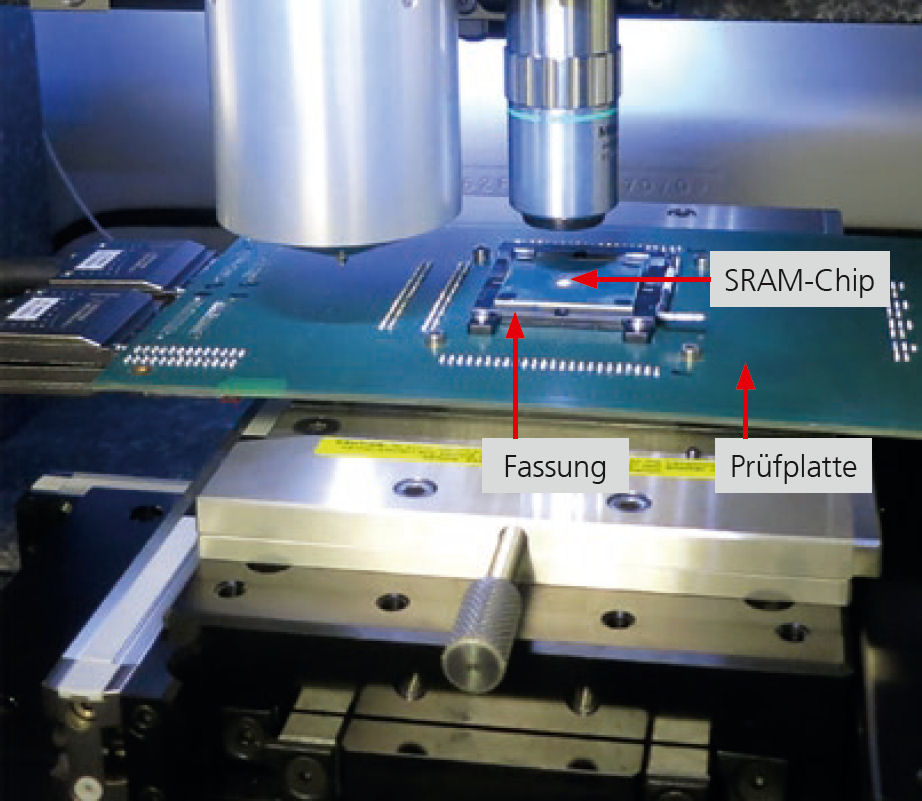

Der Ansatz erlaubt die Untersuchung von Chip-Package-Interaction (CPI), Chip-Board-Interaction (CBI) sowie die Bestimmung von möglichen Architektur-Schwachstellen in neuartigen SRAM-Schaltkreisen. Dabei werden die Chips auf einem Flip-Chip-Substrat ohne Abdeckung verbaut und das Silicium rückseitig auf 16 μm gedünnt. Für elektrische In-situ-Messungen wird der Chip vor, während und nach der Indentation verschiedener Kräfte verschaltet. Bild 1 zeigt den experimentellen Aufbau mit den verwendeten SRAM-Chips.

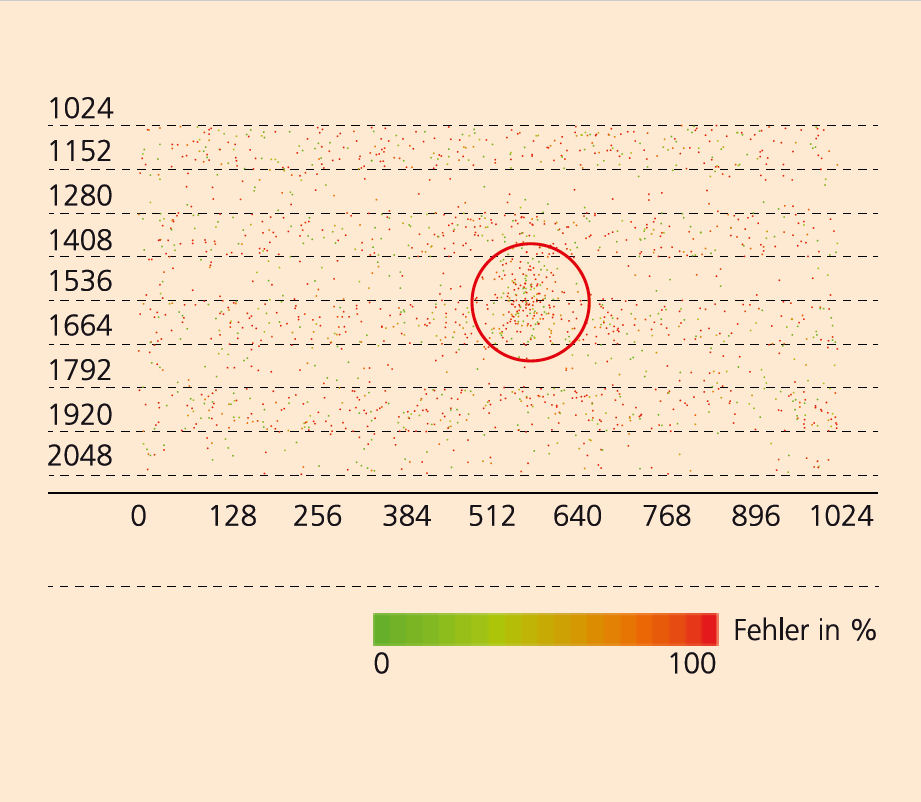

Der erste Schritt, die sphärische, elastische Nanoindentation, erfolgt an verschiedenen Stellen auf der Rückseite des Chips. Die elektrischen Messungen im zweiten Schritt beinhalten eine Lese-Stör-Prozedur und eine Fehler-Prozedur. So können unbeabsichtigte Datenänderungen, sogenannte Bit-Flips, durch aufgebrachte Belastung bestimmt werden. Für die Lese-Stör-Prozedur wird ein Schachbrettmuster eingeschrieben, wobei der Schreibschritt mit einer Unterspannung an der Bit-Flip-Schwelle erfolgt. Im anschließenden Leseschritt mit Sollbedingungen werden die Bit-Flips detektiert. Nach 50 Wiederholungen wird die Fehlerhäufigkeit mit der Belastung korreliert. Bild 2 zeigt eine Zellfehlermatrix mit zusätzlichen Störsignalen für eine angelegte Belastung von 1,3 N. Die Belastung führt zu einer deutlichen Zunahme der Zellfehler-Wahrscheinlichkeit um 40 % am Indentationsort (roter Kreis). Der Prozess ist reversibel, d. h. nach dem Entfernen der Belastung treten keine Fehler mehr auf. Die experimentell ermittelten Ergebnisse werden im letzten Schritt mit FEM-Simulationen unter Verwendung von SRAM-Layout und Schichtaufbau verglichen, um optimale Indentationsorte und Spannungs/Dehnungs-Felder zu bestimmen. Darüber hinaus eignet sich diese Testmethode für die Beurteilung mechanischer Spannung auf aktiven Transistorbereichen zur Design- Optimierung auf Chip-, Package- und Board-Level. Weitere Untersuchungen von neuen Technologien sind geplant.

Diese Arbeit entstand in Zusammenarbeit mit Volkswagen AG, GLOBALFOUNDRIES Dresden sowie dem Fraunhofer-Institut für Integrierte Schaltungen IIS, Institutsteil Entwicklung Adaptiver Systeme EAS.